| chercheursduvrai.fr |

Aide Aide

Recherche Recherche

Membres Membres

Calendrier Calendrier

|

| Bienvenue invité ( Connexion (Log In) | Inscription (Register) ) | Recevoir à nouveau l'email de validation |

To view this board in english, you must be registered.

To view this board in english, you must be registered.| Pages: (11) « Première ... 7 8 [9] 10 11 ( Aller vers premier message non lu ) |    |

|

Ecrit le: Mardi 16 Février 2016 à 21h47

|

|||

Expert(e)       Groupe: Membres Messages: 3939 Membre n°: 10047 Inscrit le: 07/11/2011 |

tant pis j'aurais proposé. ++ Je confirme le pétage de plomb de la simulation à partir de 30ms environs, même avec les ringBack.  Ce message a été modifié par BlueDragon le Mardi 16 Février 2016 à 22h34 -------------------- « No matter where you are, Look for the brightest star, Believe it is true, My soul is smiling at you", FastWalkers

|

||

|

Ecrit le: Mardi 16 Février 2016 à 23h01

|

|

Expert(e)       Groupe: Membres Messages: 255 Membre n°: 2 Inscrit le: 07/08/2002 |

Je ne sais toujours pas ce qu'est un RingBack, mais si ça ne marche pas plus, pas grave. Merci quand même. Après comment faire un truc qui marche.... Est-ce que la simul dit une chose vraie ou pas?

-------------------- "Détourne-toi des préceptes de ceux qui spéculent sur le monde, mais dont les idées ne sont pas confirmées par l'expérience."

Léonard de Vinci |

|

Ecrit le: Mardi 16 Février 2016 à 23h25

|

|

Expert(e)       Groupe: Membres Messages: 1561 Membre n°: 10313 Inscrit le: 11/03/2013 |

Ring back, sonnerie retour

je pense que l'idée est d'amortir des oscillations qui pourraient naître sur la gate du transistor. et certainement à cause de ce que je vais décrire ci dessous. En fait à ce que je viens de voir sur ma simul, lorsque le transistor du haut envoi son front, la capa entre drain et gate, du transistor du bas, laisse passer le font de tension a travers cette capa parasite et charge la gate du transistor du bas qui du coup déclenche le dit transistor. et les 2 conduisent en même temps... Pourquoi ça arrive uniquement quand il n'y a pas de charge, ça je ne sais pas encore. en tout cas ça n'arriverait pas avec un driver qui absorbe ce pic de courant. les 15 Ohms ne nous aident pas sur ce coup là. |

|

Ecrit le: Mardi 16 Février 2016 à 23h36

|

|||

Expert(e)       Groupe: Membres Messages: 3939 Membre n°: 10047 Inscrit le: 07/11/2011 |

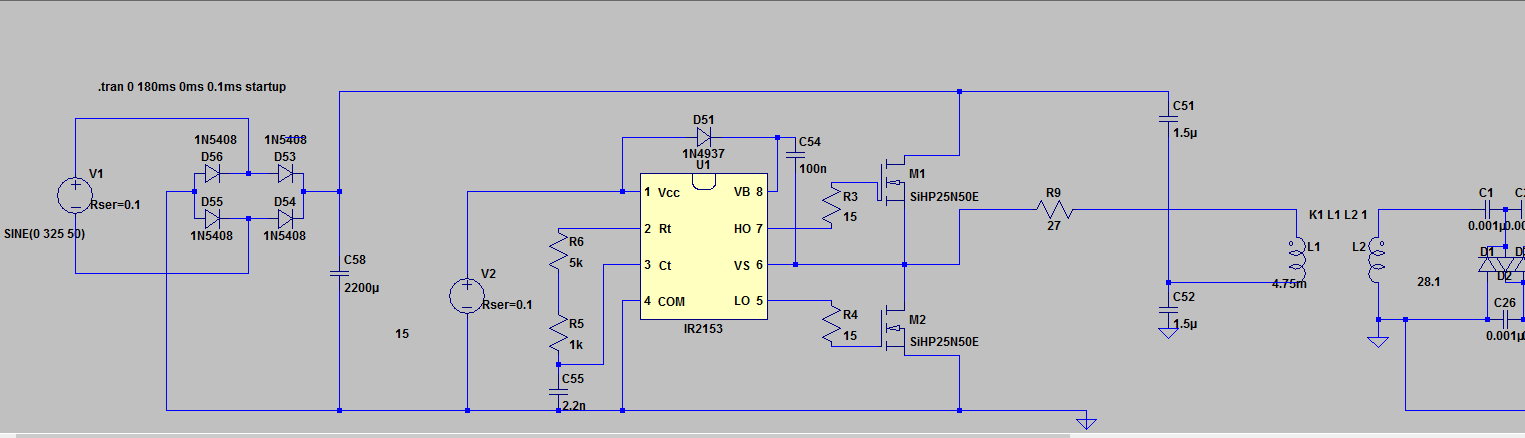

Un ring back, c'est quand la capacité interne et virtuelle de CGS résonne avec les fils du circuit dû à la coupure brute de la tension. ça créé une impulsion breve qui transforme la piste de cuivre et la capacité de Vgs en un circuit résonant. ça se traduit typiquement par une onde oscillante juste après la coupure du mosfet. Voici une image provenant d'un circuit réel (et pas d'une simulation) :  Donc quand tu met en place des MOSFET, il faut : 1/ essayer de charger au plus vite la capa de VGS, raison pour laquelle on utilise des driver qui envoient un max d'amperage 2/ essayer de décharger au plus vite la capa de VGS, raison pour laquelle on place une diode inverse en parallèle de la résistance de charge de la capa (resistance de charge qui est censé être calculée suivant ce que peut débiter le driver pour pas le griller) 3/ essayer de couper tout effet résonant "ringing effect" ou "RingBack", dû à une coupure brutale de MOSFET 4/ Maintenir un VGS en dessous de 30v, car le ringBack peut détruire le transistor, donc parfois on place une zener sur VGS 5/ Maintenir une commutation très rapide et franche du MOSFET parcequ'on évite la région ohmique comme la peste (le fameux RDSon) Bref, vois le RingBack comme un coup de bélier dans la plomberie. Le moyen de couper ça, c'est de placer une résistance dans VGS qui draine le potentiel à la masse, mais en contre-partie qui lutte efficacement contre l'effet résonant. ça fait partit des best-practices des MOSFET. La résistance de RingBack placée, j'ai de nouveau analysé le problème...et ce n'est pas du tout un problème de ringBack (par contre, il est important que vous les preniez en compte dans le schéma de base, sinon gare aux surprises plustard). Je ne sais pas me positionner totalement à dire si le problème vient de la simulation, ou si c'est un vrai problème correctement simulé C'est un problème que je n'ai jamais eu à gérer lorsque j'ai conçu mon circuit à l'époque, et il ne ressemble à rien à quelquechose de "normal". Ce que je remarque c'est que le pic intervient lorsque l'un des deux MOSFET commute. Tant que l'on est dans la periode où le MOSFET est retourné à 0v de VGS et que l'autre n'a pas commuté, le problème n'existe pas. Ce n'est donc pas un problème de DEADTIME (ou temps mort entre deux commutations, qui entraînerait un court circuit s'il n'existait pas). Comme tu l'as dis, ce pic grossi à chaque commutation, en commençant vers les 200mv en début de simu, pour atteindre les 4v de Vgs vers 25ms, ce qui correspond au VGSThreshold minimum pour faire commuter le MOSFET. Je remarque également que ce problème est valable sur les deux VGS de MOSFET, ce qui n'est pas anodin, car celà implique donc que quelquechose sort de l'IR2153 en terme d'ampérage pour aller charger la Gate. Avant donc de pousser la parano trop loin, je vais appliquer une autre bonne pratique des professionnels avec les MOSFET, la mise en place d'une diode de commutation extrêmement rapide (type MUR120) en parallèle de la diode intégrée à l'IRFP450. C'est un best-practice que j'avais lu à l'époque et qui ne mange pas de pain : en effet, dans le doute, j'applique systématiquement l'ensemble des best-practice de Design que j'avais regroupé à l'époque. On verra si ça résoud le problème, même si ça joue sur un facteur qui ne semble avoir aucun lien dans un premier temps. La simulation est lancée, et le fichier attaché.  Edit : Mettre les MUR120 a déplacé légerement le problème....  Le pic qui fait penser à un RingBack, mais qui n'en est pas un... quelquechose entraîne un VGS qui fait commuter le MOSFET, mais impossible de dire ce que c'est ! la simulation de l'IR2153 serait-elle bugguée ? Il faut remplacer la simulation du 2153 par un autre (2110 ou autre) pour vérifier. On peut garder toutes les valeurs des composants et juste changer le driver dans un premier temps.  Ce message a été modifié par BlueDragon le Mercredi 17 Février 2016 à 00h05 Fichier joint ( Nombre de téléchargements: 0 )  Dragon.asc (25.23 Ko)

Dragon.asc (25.23 Ko)-------------------- « No matter where you are, Look for the brightest star, Believe it is true, My soul is smiling at you", FastWalkers

|

||

|

Ecrit le: Mercredi 17 Février 2016 à 09h31

|

|

Expert(e)       Groupe: Membres Messages: 1561 Membre n°: 10313 Inscrit le: 11/03/2013 |

Tout ce que tu dis BlueDragon est intéressant pour moi qui n’ai jamais eu l’occasion d’étudier les alimentations à découpage très a fond.

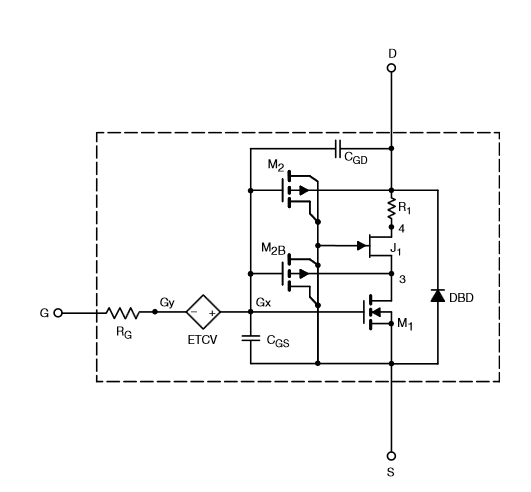

C’est tout un monde qui s’ouvre et un monde de terminologies aussi. Clairement tous les problèmes viennent du 2153 qui n’est pas capable de bien absorber le courant. Est-ce le bon modèle du 2153 ou pas, c’est encore un autre problème. Toutes les best practice ne sont que des pis aller pour faire fonctionner de mauvais driver. Le driver aurait un comportement "idéal", il n'y aurait pas besoin d'artifices pour que l'ensemble fonctionne. Ce que je disais hier, en peut être plus clair :  En 1, le transitor du bas est bloqué, VGS= 0V. Le transistor du haut commute les 325V. En 2, CGD+CGS constitue un pont diviseur capacitif Il passe du courant dans le pont capacitif lors du front En 3, ce courant charge CGS et du coup VGS grimpe au delà du seuil et le transistor du bas conduit (c’est là notre drame En 4, l’IR2153 qui devrait faire en sorte que VGS reste à 0V et donc absorber le courant qui vient de CGD n’y parvient pas. D’une part à cause de la 15 Ohm et d’autre part a cause de la capacité de l’IR2153 à absorber du courant en dehors des fronts de commutations. On a vu que les drivers sont capable d’émettre ou absorber beaucoup de courant lors des fronts mais qu’en dehors de ce moment particulier, ils ne sont pas capable de la même prouesse. Voici le courant et la tension en LO pin5 de l’IR2153 au moment où le transistor du haut commute le 325V :  C’est clairement l’IR2153 qui n’est pas capable d’absorber le courant qui est en train de charger la gate du transistor du bas. D’après les valeurs pic, V LO en vert 4.36V et I LO en bleu clair 0.242 A, on en déduit un résistance interne pour l’IR2153 de 18 Ohm. J’ai fait une simul avec 1 Ohms au lieu de 15 Ohm sur les gates et le résultat est le même. C’est l’IR2153 qui pose le problème avec ces 18 Ohm internes. Quant à l’explication pourquoi le problème lorsqu’il n’y pas de charge ? J’avancerais (pas vérifié) que lorsqu’il y a une charge la tension VDS doit monter plus lentement, du coup le courant dans le pont capacitif CGD+CGS est moindre. et du coup on atteint pas le seuil de commutation du transistor du bas et tout va bien. Si le modèle est juste, la seule solution que je vois est soit de changer de transistor pour un transistor a capa de gate plus faible, il y aura moins de courant a absorber, soit de consommer lors des transitions et c'est certainement le role du RC que j'ai oté très rapidement, ne comprenant pas quel en était l’intérêt. Visiblement, c'est un métier les alimentions a découpage Schéma du transistor tiré de http://didier.magnon.free.fr/cours/commuta...0chapitreIV.pdf qui est intéressant par ailleurs. |

|

Ecrit le: Mercredi 17 Février 2016 à 10h24

|

|||||

Expert(e)       Groupe: Membres Messages: 255 Membre n°: 2 Inscrit le: 07/08/2002 |

On va se rejoindre. J'ai fouillé un peu sur le site Russe qui donne le modèle. Le gars l'a élaboré en lisant le datrasheet et a dit que tout ce qui manquait il m'a inventé. A priori il y a eu de nombreux bugs et à un moment donné les gens qui s'en servaient en simul en comparant au vrai disaient "ok" et donc il a diffusé. Mais son truc est fait comme il peut et n'est donc pas un vrai modèle. Du coup on ne peut absolument pas faire confiance à ce qu'on obtient par la simul. ça marche en gros mais pas forcément dans le détail: https://translate.googleusercontent.com/tra...ZQ_ASRlpnhe7wmQ Je tentais de comprendre comment est construit le modèle de circuit, comment marche un modèle LTSPice de .subckt. Tes 18 ohms on les voit dans la fin du modèle:

Ils sont là tes 18 ohms: .MODEL SVL VSWITCH (RON=18 ROFF=.1meg VON=2.45 VOFF=2.5) Il a modélisé des interrupteurs qui ont 18 ohms de résistance interne quand ils sont en circuit fermé (et 0.1Meg ohm quand ils sont ouverts) et ils sont utilisés là: S1 HO VS CdlyH_P COM SVL S4 LO COM CdlyL_P COM SVL Donc ils sont implémentés dans les interrupteurs qu'il appelle S1 et S4 qui correspondent à une connexion entre HO et VS et S4 entre LO et COM. Tu as mesuré celui du S4 avec ton test. Comme tu le comprends bien, on peut parfaitement changer la mesure de la résistance interne de 18 ohms par la valeur qu'on veut en le changeant dans le fichier de définition du modèle. La vraie question est: est-ce que ces 18 ohms sont justifiés par rapport au datasheet (seule source d'info que le gars a utilisé pour construire le modèle, il a mis ce qu'il avait envie de mettre pour ce qui n'y était pas)? On regarde le datasheet: http://www.promelec.ru/pdf/ir2153.pdf Moi je ne vois rien dans le datasheet qui justifie cette résistance. De la même façon il a choisi une résistance interne de 35 ohms pour les interrupteurs modèle entre VB et HO et aussi entre Vcc et LO. En fait si la doc ne dit rien il a mis ce qu'il voulait et qui lui a semblé être en accord avec certaines mesures faites sur le circuit réel... jusqu'à preuve du contraire. On a peut être juste montré le contraire, à savoir que ces valeurs sont fausses et ne correspondent pas au vrai. Donc seul moyen de savoir? C'est de faire le montage en vrai. C'est un problème quand même? En même temps comme le souci n'est pas sensé exister... il est probable que la simul soit donc complètement fausse. Donc on peut mettre 1 ohm si tu veux au lieu de 18. On fait comme on veut, il suffit de changer dans le fichier! Le truc est de savoir quelles sont les vraies valeurs. Du coup il faudrait acheter un vrai composant et faire de petits circuits de tests pour mesurer les résistances qu'on a besoin de connaitre en vrai!! D'ailleurs le concepteur du circuit le dit en russe dans son forum:

Il n'a pas les courants de sortie Lo et HO dans la fiche technique! -------------------- "Détourne-toi des préceptes de ceux qui spéculent sur le monde, mais dont les idées ne sont pas confirmées par l'expérience."

Léonard de Vinci |

||||

|

Ecrit le: Mercredi 17 Février 2016 à 10h37

|

|

Expert(e)       Groupe: Membres Messages: 255 Membre n°: 2 Inscrit le: 07/08/2002 |

Ici un autre datasheet pour la version avec bootstrap inclus, page 5:

http://radiolux.com.ua/files/pdf/IRS2153.pdf On y trouve que le courant pouvant être donné par HO et LO est de 180mA en sortie du circuit intégré et 260mA en entrant. C'est ce qu'a indiqué le concepteur du circuit dans le Russe mal traduit du message précédent que je comprends mieux. Il dit qu'il faut donc avoir une résistance équivalente totale de l'ordre de 50 ohms entre l'interne qu'il a mise et ce qu'on ajoute en externe (sur du 12V 50 ohms donne 240mA) pour arriver à ces courants. Au final avec nos 15ohms et ses 18 ohms on est même au-dessous de la réalité. Donc le IR2153 peut encore moins bien que ce qu'on a déjà si on suite cette idée. Donc même si la simul n'est pas parfaite, elle est encore mieux que ce qu'on aurait? Ce message a été modifié par P. le Mercredi 17 Février 2016 à 10h43 -------------------- "Détourne-toi des préceptes de ceux qui spéculent sur le monde, mais dont les idées ne sont pas confirmées par l'expérience."

Léonard de Vinci |

|

Ecrit le: Mercredi 17 Février 2016 à 10h57

|

|

Expert(e)       Groupe: Membres Messages: 1561 Membre n°: 10313 Inscrit le: 11/03/2013 |

Oui depuis la début je trouvais étrange qu'ils n'affichent pas les courants.

c'est le premier truc que je regarde dans la datasheet .j'ai conclu en disant qu'il fallait faire confiance aux temps de commutations... Maintenant je comprends, il n'y a pas de quoi être fier de ces valeurs de courant, elles sont ridiculement basse ! Nous voilà confronter à ma première signature Visiblement le modèle est juste pour les bas niveaux: Isink mais pas pour le I source. Ou on reste sur ce circuit simple et on adapte autours, c'est à dire en utilisant des transistors à faible capa de gate. ou on passe à autre chose ? Je vais tenter les vishay que tu avais trouvé P. |

|

Ecrit le: Mercredi 17 Février 2016 à 10h59

|

|

Expert(e)       Groupe: Membres Messages: 255 Membre n°: 2 Inscrit le: 07/08/2002 |

En fait tu as mesuré 4,4V en VO. Donc si on veut arriver à nos 260mA absorbables au max (et là c'est le max du max), cela fait une résistance de 17 ohms au total.

Donc avec la 18 ohms de résistance et 0 ohm en résistance externe on arrive à quasiment le max possible. Sinon on met 2 ohms internes et on laisse la 15 externe et c'est pareil. Dans tous les cas ça ne s'arrange pas. Si tu sais comment régler ça en remettant ce que tu as enlevé du schéma d'origine, c'est une bonne idée -------------------- "Détourne-toi des préceptes de ceux qui spéculent sur le monde, mais dont les idées ne sont pas confirmées par l'expérience."

Léonard de Vinci |

|

Ecrit le: Mercredi 17 Février 2016 à 11h03

|

|||

Expert(e)       Groupe: Membres Messages: 255 Membre n°: 2 Inscrit le: 07/08/2002 |

Alors souci avec les Vishay que j'avais trouvé. J'avais importé le modèle Spice qu'ils ont écrit sur leur site Vishay et il était reconnu par LTSPice IV, pas de soucis. Le problème est que la simul tourne sur deux alternances avec les MOSFET et ensuite tout bloque. Il doit y avoir une erreur dans leur fichier modèle Spice d'un truc pas bien reconnu par LTSpice en importation en tous cas. Et comme je n'y connais rien sur la modélisation, lme langage utilisé par eux, du coup j'avais regardé ça il y a 2 ou 3 jours et pas pu décoincer le problème. Donc on a un modèle Spice, il tourne, mais deux alternances, donc on ne dépasse pas les micro secondes de calcul!! En fait il tourne bien sur la partie des premières millisecondes où les MOSFET ne commutent pas encore. Bref souci technique là. Mais bon ça doit pouvoir se décoincer en passant les 100h qu'il faut pôur apprendre à savoir lire et écrite les modèles LTSpice avec leur lange dont je ne trouve pas de doc claire sur le net... -------------------- "Détourne-toi des préceptes de ceux qui spéculent sur le monde, mais dont les idées ne sont pas confirmées par l'expérience."

Léonard de Vinci |

||

|

Ecrit le: Mercredi 17 Février 2016 à 11h22

|

|

Expert(e)       Groupe: Membres Messages: 3939 Membre n°: 10047 Inscrit le: 07/11/2011 |

Belle trouvaille Mr P., bravo. Tes notions de physique sont très utile et clairement, on peut dire que LTSpice est un très bon simulateur comme le mentionné Zgreudz.

-------------------- « No matter where you are, Look for the brightest star, Believe it is true, My soul is smiling at you", FastWalkers

|

|

Ecrit le: Mercredi 17 Février 2016 à 12h56

|

|

Expert(e)       Groupe: Membres Messages: 1561 Membre n°: 10313 Inscrit le: 11/03/2013 |

Je suis parti du modèle pour irfp450.

J’ai renommé le .txt du zip en SiHP25N50E.spi Je l’ai copié ici :LTC\LTspiceIV\lib\sym\extra\irf\lib, comme pour l’irfp450. et suis parti du .asy de l’irfp450 que j’ai renommé en SiHP25N50E.asy Puis j’ai édité ce nouveau .asy en changeant le nom de marquage dans le symbole. J’ai croisé les doigts (très important) et ça fonctionne sur autant de périodes que l’on veut. Mais rien de magique pour l’instant quant a une solution. Fichier joint ( Nombre de téléchargements: 3 )  SiHP25N50E.spi (1.62 Ko)

SiHP25N50E.spi (1.62 Ko) |

|

Ecrit le: Mercredi 17 Février 2016 à 12h59

|

|

Expert(e)       Groupe: Membres Messages: 1561 Membre n°: 10313 Inscrit le: 11/03/2013 |

|

|

Ecrit le: Mercredi 17 Février 2016 à 13h42

|

|

Expert(e)       Groupe: Membres Messages: 255 Membre n°: 2 Inscrit le: 07/08/2002 |

@eclecton

Oui, j'avais fait comme toi: repris le fichier symbole de l'IRFP450 et changé le nom, et inclus le fichier txt du composant donné par Vishay en le renommer en sub. J'ai aussi utilisé les fichier .lib au lieu du .txt du modèle Vishay (car on peut lier au fichier qu'on veut avec le .asy, suffit der changer le code du fichier texte); et essayé les diverses versions de fichier qu'ils donnent, il y en a 3. Dans tous les cas ça ne marchait que quelques alternances. C'est pour ça que je n'ai pas diffusé les fichiers ici tant que je n'avais pas trouvé de solution à ce que ça marche. Comme je n'avais pas le temps de chercher, j'ai mis de côté. @BlueDragon C'est gentil, mais franchement je n'ai rien trouvé de spécial. J'ai justement regardé comment c'était écrit et pas compris. Donc il y a tout à apprendre pour en faire un truc utile. Mais oui LTSpice est puissant en effet. -------------------- "Détourne-toi des préceptes de ceux qui spéculent sur le monde, mais dont les idées ne sont pas confirmées par l'expérience."

Léonard de Vinci |

|

Ecrit le: Mercredi 17 Février 2016 à 17h48

|

|

Expert(e)       Groupe: Membres Messages: 1561 Membre n°: 10313 Inscrit le: 11/03/2013 |

A la réflexion le RC en // du transfo est là pour absorber les surtensions avec des charges inductives.

En effet on a coupure brutale de courant pendant le dead time et si la charge est selfique, on a un fort dV qui pourrait être préjudiciable aux transistors. Ici un montage pour des plaques d’induction, on y voit le roi des RC http://danyk.cz/induk2.png ----------- Concernant le problème de courant qui passe entre les 2 transistors, je commence à intégrer les good practice de BlueDragon. La seule solution que j’ai trouvé qui n’est pas une vraiment une good practice à mon avis, c’est ajouter le capa sur la gate 6.8nF voire 10nF, pour absorber le courant venant de CGD. Et de diminuer la résistance de gate à 0 pour ne pas trop penaliser les temps de montée et descente. Ça ne me satisfait pas du tout car c’est transférer le problème de commande de lIR2153 sur les transistors qui voient leurs temps de montée et descente augmentés et du coup dissipent plus qu’ils ne devraient. Mais ça reste acceptable pour les transistors. 18W et 17W, avec la sortie a vide. Je n’ai pas fait en charge car j’ose espérer qu’en réalité et non en simul, il n’y a pas ce problème.voir à la fin. Ici avec 1 Ohm et 10nF, j’ai perdu les courbes mais ça fonctionne dans le principe. Il peut y avoir des problèmes de puissance en charge et dans R9.voir à la fin Sans R9 les courants sont vraiment importants à cause du cockcroft.  -------- J’ai fait un peu le tour des schémas qui circulent avec l’IRF2153 pour voir s’ils rencontrent le problème que nous avons en simul et voir comment ils utilisent le circuit. A première vue le circuit donne satisfaction. Contrairement à amazing, ici avec ajout d’une limitation de courant qui stoppe l’oscillateur plutôt que stopper sur l’alimentation du 2153. http://320volt.com/wp-content/uploads/2008/08/etd34_smps.jpg Certains suppriment les résistances de 15 Ohms sur les gate. http://obrazki.elektroda.net/22_1219501734.gif Certains l’utilisent en pusch pull plutôt qu’en half bridge, sans resistance de gate non plus. note: les capa en // des transitors doivent être là pour arrondir le carré. http://danyk.cz/menic230_4.png En conclusion le modèle de simul du 2153 ne doit pas être juste puisque des gens l’utilisent sans précaution particulière. Il est vrai qu'en général ils utilisent des transistor avec moins de capa de gate que nous et donc plus de RDSon. ce sont des montages un peu moins puissants, donc tout va bien pour eux. En perspective, le fait d’ajouter des résistances en série avec les diodes dans le cockroft va limiter le courant lors de la charge, ce qui fait que nous pourrons sans doute nous passer de R9. et tout devrait bien se passer........ou pas Faudrait tester à vide, puisque c'est là le problème à priori et éventuellement mesurer ce qui se passe sur les sorties du driver en vue de corriger le modèle. |

|

Ecrit le: Mercredi 17 Février 2016 à 19h09

|

|||

Expert(e)       Groupe: Membres Messages: 255 Membre n°: 2 Inscrit le: 07/08/2002 |

Ce qui revient à dire que l'impédance de l'ensemble R+C // L est très forte vue de l'extérieur, petit courant dedans, car le courant s'échange entre le R+C et le L. Donc c'est un circuit RLC accordé sur la fréquence de résonance qui est utilisé, ce que j'avais dit au début au final? ça sert à créer un circuit bouchon. Sinon pour le reste, donc la modif du circuit c'est quoi au final, car tu parles du RC mais tu ne l'as pas mis sur ton schéma? Par contre il y a les 10nF que tu ajoutes dessus. Je vois que tu as mis les transistors HP25N50E sur ton schéma alors que la simul ne marche pas? Donc c'est quoi le schéma en fin de compte? Je ne pense pas que la simul du circuit ne marche pas, car le gars a inventé les valeurs qu'il n'avait pas, mais cela pour le courant des HO et LO et donc tant que ce courant correspond à la limite donnée du datasheet ça reste bon. La cascade cockroft ne consommera pas pas beaucoup à vide (même presque rien) que j'y mettre les résistances ou pas dedans pour les diodes n'y changera rien. Donc je ne vois pas pourquoi ça règle un souci qui reste toujours là. Tant qu'en simul ça ne marche pas, et avec aucun contre argument valable finalement contre la simul du circuit qui existe pour le IR2153, on ne peut pas dire que ça va marcher en vrai; pas d'accord pour faire comme ça. C'est s'exposer à un truc qui ne fonctionne pas. Justement on ne se lance dans l'opération que si elle peut marcher; pas si déjà sur le papier (ou l'ordi en l'occurence) ça ne marche pas. Question de pas acheter pour des centaines d'euros de matériel et avoir rien qui tourne ensuite. Bref si tu arrives à faire tourner la simul avec des changements de paramètres qui permettent de détourner le souci c'est super. Mais il faut que la simul tourne en tous cas. Tu la fais tourner comment avec les HP25N50E!?? -------------------- "Détourne-toi des préceptes de ceux qui spéculent sur le monde, mais dont les idées ne sont pas confirmées par l'expérience."

Léonard de Vinci |

||

|

Ecrit le: Mercredi 17 Février 2016 à 19h47

|

|||

Expert(e)       Groupe: Membres Messages: 255 Membre n°: 2 Inscrit le: 07/08/2002 |

Rectif: la simul ne bloque pas avec les HP25N50E, elle avance si lentement que je crois qu'elle bloque: elle avance de 0,0001 micro secondes de simul toutes les 5 à 10 secondes de temps réel environ. La courbe graphique se complète si on attend plusieurs minutes, elle se complète de quelques nouveaux points. Alors que les premières microsecondes se font instantanément. En fait j'avais mal lu ton post où tu mettais tes fichiers, je pensais que tu disais que toi aussi ça ne tournait que quelques alternances. En fait tu dis le contraire? Donc chez toi ça marche et chez moi pas. J'ai repris les fichiers que tu as mis à charger en fichier attaché. Puisqu'ils sont exactement la même chose que ce que j'avais déjà fait avant (en fait j'ai testé les 3 versions du fichier, celui que tu mets est la première version), bien sûr n'a pas marché mieux. Je ne peux faire tourner aucune simul avec les HP25N50E du modèle actuellement dispo. Donc là pour le moment tu es le seul à faire tourner une simul avec semble-t-il. Je me demande comment, on a le même logiciel LTSpice IV, la même version, et avec les mêmes fichiers de modèle. Voir si BlueDragon est bloqué comme moi. Quand j'arrête la simul, une fois tous les 36 il me pond un rapport indiquant les erreurs qu'il trouve dans le fichier de modèle donné justement:

Comme il le dit ce sont des instructions non reconnues, pas sûr que ça soit une erreur en soit, juste LTSpice n,'exploite pas ces paramètres. -------------------- "Détourne-toi des préceptes de ceux qui spéculent sur le monde, mais dont les idées ne sont pas confirmées par l'expérience."

Léonard de Vinci |

||

|

Ecrit le: Mercredi 17 Février 2016 à 19h57

|

|

Expert(e)       Groupe: Membres Messages: 1561 Membre n°: 10313 Inscrit le: 11/03/2013 |

Non pas de RC car notre charge est capacitive : le cokcroft.

Dans la pratique il en faudra peut être car le câblage amène toujours des self parasites que l’on a pas en simul. Reste à savoir l’ampleur ? Il n’y a que la mesure in situ qui dira. Les résistances en série avec les diodes vont arranger des choses, elles vont limiter le courant lors de la charge du cockroft. Courant que je limite actuellement avec R9. Tout ça pour que les transistors aient des courant acceptables. Dans la pratique il faudra peut être un peu de R9 mais moins qu’actuellement et c’est mieux pour elle car elle se prend un paquet de Watts en ce moment. Mais ça n’a aucun rapport avec le souci de courant entre les 2 transistors, c’est juste un autre problème. Je n’ai pas dit qu’on allait faire ce schéma, surtout pas, j’ai dit qu’il serait intéressant de vérifier en pratique la modélisation des sorties de l’IR2153, ce que tu avais proposé. Et vérifier s’il y a bien ces pics de tension sur VGS dans la vraie vie. Je ne propose aucun schéma définitif avec l’IR2153, il faut encore explorer. La solution de mettre de la capa sur la gate ne me satisfait pas car les transistors dissipent à cause de ça. Les transistors HP25N50E sont là car ils ont moins de capa de gate et permettent de passer plus de courant, ce qui est favorable pour la diminution de R9, ce qui est favorable à l’obtention de 500KV en sortie. 500KV que l’on n’atteindra pas si R9 est trop grande. Dans l’idéal il ne faudrait pas de R9 pour avoir 500KV en charge 500W . et pas de R9 implique des courant de folie lors de la charge du cockroft s’il n’a pas de résistance en série avec les diodes. Il y a 3 problèmes différents : -Le courant entre les 2 transistors à cause du 2153 qui a un mauvais I sink, à priori vu la datascheet en Rev A qui est la seule à donné les courants. Maintenant ils sont en Rev O et conseillent d’utiliser l’IRS2153D, je viens de le voir….pourtant en rouge …Mais bon on est pas mieux renseigné sur les courants. On a juste les temps de montée et descente sur 1nF, et sous 14V. Normalement un temps de montée se mesure de 10% à 90%. On peut faire une approximation de la sortie avec une résistance mais pas certain que la sortie soit linéaire et que du coup l’approximation soit juste. D’où la mesure des sorties - Le courant dans les transistors lors de la charge du cockroft à cause des capa du cockroft. - Le RC en cas de charge inductive, vu qu’il y a des ruptures de courant pendant le dead time. |

|

Ecrit le: Mercredi 17 Février 2016 à 20h04

|

|

Expert(e)       Groupe: Membres Messages: 1561 Membre n°: 10313 Inscrit le: 11/03/2013 |

je viens de vérifier la simul en supprimant de .spi du 450.

La simul utilise le fichier spi de l'irfp450............ donc pas bon du tout. je ne sais pas comment lier le .asy au .spi. en fait je n'ai jamais fait tourner autre chose que l'irfp450. retour case départ! |

|

Ecrit le: Mercredi 17 Février 2016 à 20h13

|

|||

Expert(e)       Groupe: Membres Messages: 255 Membre n°: 2 Inscrit le: 07/08/2002 |

Tu édites ton fichier .asy que tu avais fait pour ton HP25N50E et là où il y a le nom du modèle dedans, tu remplaces par celui du HP25n50E:

C'est cette ligne là qui fait le lien: SYMATTR SpiceModel SiHP25N50E.spi J'ai mis "SiHP25N50E.spi", mais tu peux l'appeler aussi "SiHP25N50E.sub" ou encore "SiHP25N50E.lib" Dans ce fichier là tu mets le code txt donné par Vishay. Et normalement tu as le même soucis que moi. En fait il faut comprendre comment sont écrits les fichiers de modélisation LTSPice pour modifier ce qui pose souci. J'étudie la question... http://ltwiki.org/LTspiceHelp/LTspiceHelp/M_MOSFET.htm https://people.rit.edu/lffeee/Intro_to_LTSPICE.pdf http://ecee.colorado.edu/~bart/book/book/chapter7/ch7_5.htm Mais pas encore compris. Il n'y a pas de ressource que j'ai pu trouver qui explique la syntaxe précise et complète du langage qui sert à faire les modèles LTSPice. C'est ça que je cherche, pour corriger les erreurs du fichier Vishay et rendre compatible avec LTSpice IV. -------------------- "Détourne-toi des préceptes de ceux qui spéculent sur le monde, mais dont les idées ne sont pas confirmées par l'expérience."

Léonard de Vinci |

||

|

Ecrit le: Mercredi 17 Février 2016 à 21h30

|

|||

Expert(e)       Groupe: Membres Messages: 3939 Membre n°: 10047 Inscrit le: 07/11/2011 |

-------------------- « No matter where you are, Look for the brightest star, Believe it is true, My soul is smiling at you", FastWalkers

|

||

|

Ecrit le: Mercredi 17 Février 2016 à 21h52

|

|||

Expert(e)       Groupe: Membres Messages: 255 Membre n°: 2 Inscrit le: 07/08/2002 |

Je commence à réussir à décoder le modèle en fonction du schéma électrique donné en modèle (ça aide!!):  Code modèle associé:

-------------------- "Détourne-toi des préceptes de ceux qui spéculent sur le monde, mais dont les idées ne sont pas confirmées par l'expérience."

Léonard de Vinci |

||

|

Ecrit le: Mercredi 17 Février 2016 à 21h54

|

|||||

Expert(e)       Groupe: Membres Messages: 255 Membre n°: 2 Inscrit le: 07/08/2002 |

Ah punaise, merci; oui voilà c'est ça qu'il me faut. le décodage de la suite de ce que je n'ai pas déduit pas observation va enfin se faire grâce à des instructions documentées. Merci!! -------------------- "Détourne-toi des préceptes de ceux qui spéculent sur le monde, mais dont les idées ne sont pas confirmées par l'expérience."

Léonard de Vinci |

||||

|

Ecrit le: Mercredi 17 Février 2016 à 22h44

|

|||

Expert(e)       Groupe: Membres Messages: 255 Membre n°: 2 Inscrit le: 07/08/2002 |

Bon alors il y a une chose dans le modèle VISHAY qui n'existe nulle part dans les docs: le ETCV et ITCV, etc. J'ai carrément supprimé du modèle. J'ai aussi modifié pour que le modèle soit celui du dessins, il y avait une interversion au niveau du J1 et R1 pour que ça corresponde. J'ai aussi supprimé les éléments non reconnus par LTSPICE (donc pas utilisés) et on arrive au modèle simplifié suivant:

Le modèle tourne toujours, plus d'erreur mais ça tourne aussi lentement qu'avant. Le fichier log indique comme avant qu'il y a un souci lors des calculs: "Heightened Def Con from" apparait partout Après recherche ça indique un problème de convergence des calculs et donc un ralentissement énorme du moteur de simulation LTScice (ce qui se passe). Mais là le modèle du fichier je le comprends et il correspond bien à leur schéma. Donc si ça ne marche pas c'est juste que leur modèle est trop complexe, même si il représente au mieux leur MOSFET. Il conduit à des calculs infernaux pour le moteur LTSPICE. Donc demain je referai un modèle ultra simplifié du MOSFET de façon plus classique, comme je l'avais vu ailleurs. Pour ce soir c'est fini. Du coup maintenant je vais pouvoir mieux lire et comprendre les fichiers modèles, c'est déjà ça. -------------------- "Détourne-toi des préceptes de ceux qui spéculent sur le monde, mais dont les idées ne sont pas confirmées par l'expérience."

Léonard de Vinci |

||

|

Ecrit le: Jeudi 18 Février 2016 à 00h48

|

|||

Expert(e)       Groupe: Membres Messages: 255 Membre n°: 2 Inscrit le: 07/08/2002 |

Finalement je m'y suis remis avant de me coucher Après avoir bien épluché la doc, cherché ce que signifiaient les différentes infiormations à compléter et regardé les modèles déjà dans la base de donnée LTSPice pour voir lesquels sont demandés, voici le modèle simplifié que j'ai construit pour le SiHP25N50E:

D'après datasheet: http://www.vishay.com/docs/91626/sihp25n50e.pdf à ajouter simplement dans la base de données des MOSFET dans le fichier "TspiceIV\lib\cmp\standard.mos" Puis ajouter un composant NMOS depuis la liste des composants et choisir le SiHP25N50Edans la liste. Voir ici pour mes sources de compréhension des coefficients: http://www.magma.ca/~legg/SR5/LTspice_buil...VDmos_model.pdf http://www.simonbramble.co.uk/lt_spice/lts..._tutorial_6.htm https://en.wikipedia.org/wiki/Power_MOSFET J'ai lancé une simulation avec la cascade à vide et l'ancienne version du circuit (pas de modif de plus depuis mes dernières simul que changer les MOSFET) -------------------- "Détourne-toi des préceptes de ceux qui spéculent sur le monde, mais dont les idées ne sont pas confirmées par l'expérience."

Léonard de Vinci |

||

|

Ecrit le: Jeudi 18 Février 2016 à 00h50

|

|

Expert(e)       Groupe: Membres Messages: 255 Membre n°: 2 Inscrit le: 07/08/2002 |

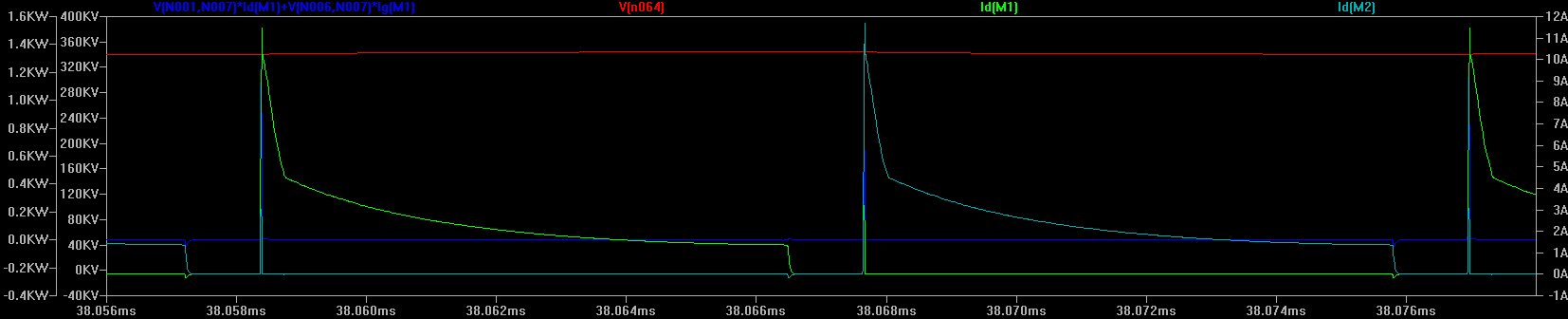

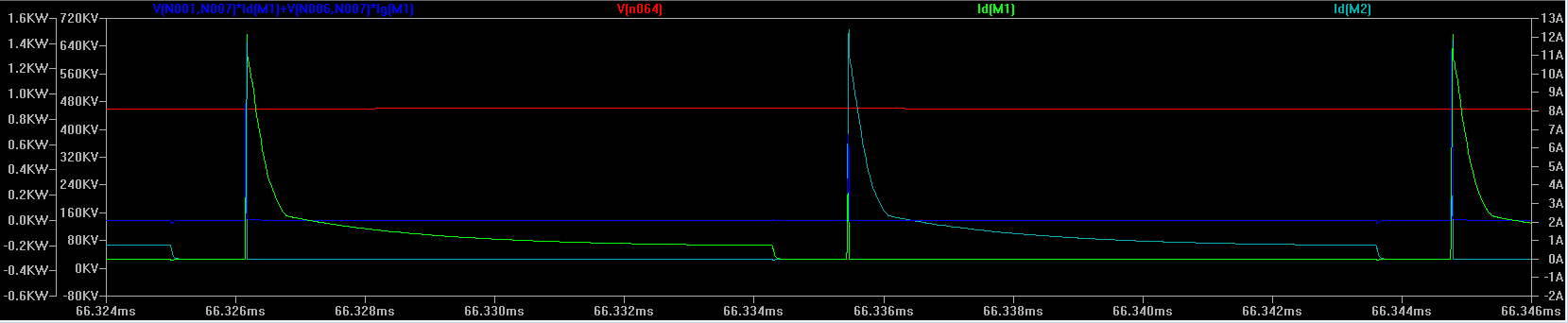

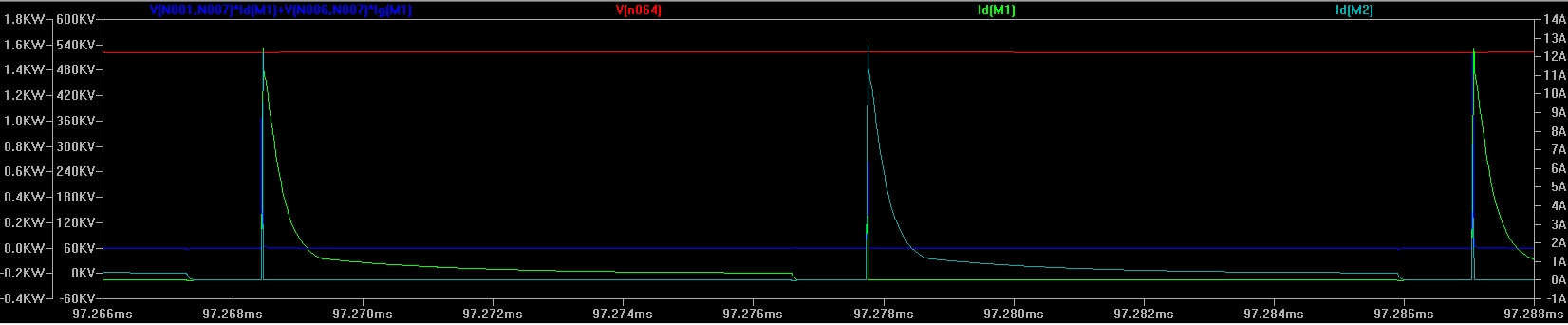

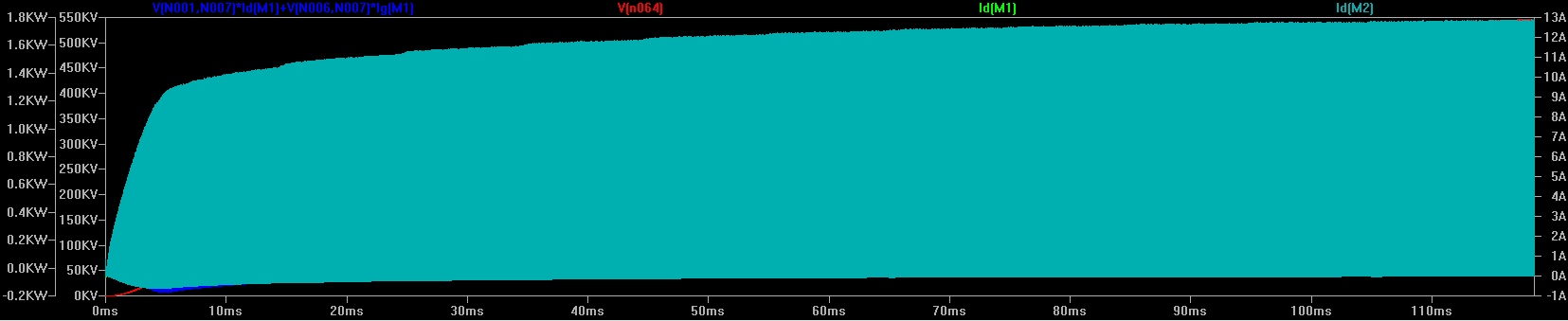

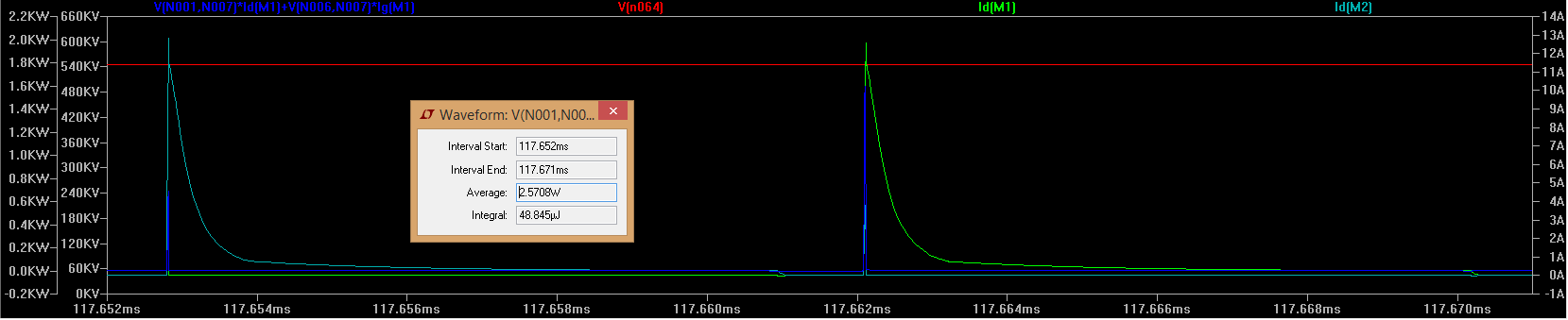

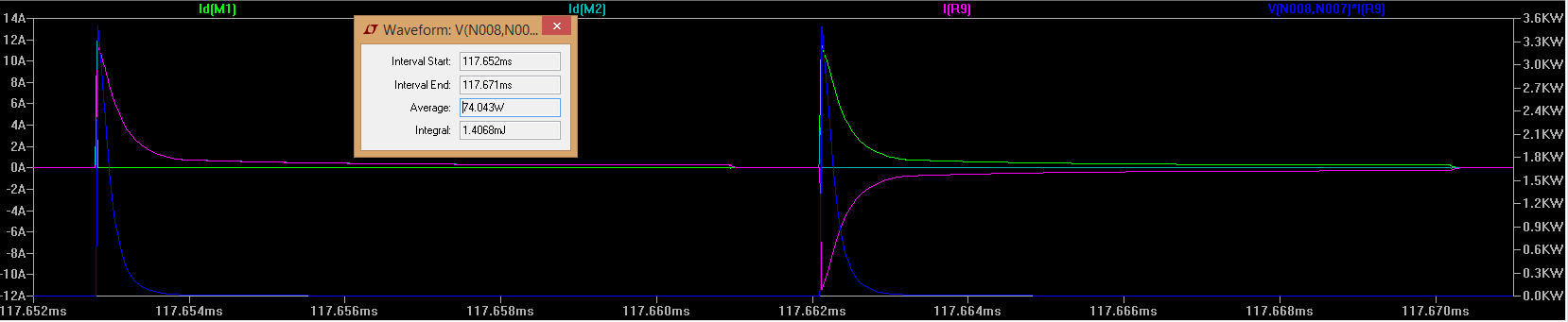

Voilà ce que ça donne en simul détaillée:

En vert le courant Drain-Source du transistor du haut, en bleu clair celui du transistor du bas. On voit des pics ponctuels à 11,5A. En bleu foncé la puissance totale dissipée dans le transistor du haut. On voit des pics ponctuels à 1,2kWatts En rouge la tension sur la résistance de 500G ohms de sortie de la cascade, chargée à 340kV. Si je vais plus loin dans le temps, même code de couleur:  Pic de courant à 12A et pic de puissance à 1,4KW, cockroft chargée à 460kV Encore plus loin:  cockroft à 523kV. Courant d epic à 12,5A et puissance de pic à 1,5kWatts. L'ensemble parait stabilisé vers 120ms environ, ou presque (je coupe la simul pour me coucher):  La puissance dissipée en moyenne dans les transistors est de 2,6Watts, je trouve ça faible quand même:  J'enlève des choses et ne garde que le courant dans les deux transistors en vert et bleu clair, j'ajoute le courant dans R9 en violet et la puissance dissipée dans R9 (bleu foncé):  On voit que le courant de R9 est exactement le courant qui passe dans les transistors quand ils sont passants (en superposé pour le premier, car dans le même sens, on confond les deux courbes, en opposition pour le deuxième, sens opposé). Plus de gaspillage de courant de court-circuit ici! La puissance dans R9 est de 74Watts dissipés en moyenne! ça a l'air de bien tenir. Donc c'est le modèle du transistor seulement qui a été changé. Après si il faut ajouter la capa de gate je ne sais quoi et remettre le circuit RC sur l'inductance du primaire c'est bien, aussi je ne sais pas pourquoi les valeurs que j'avais mises pour les inductances primaire et secondaire ont été modifiées aussi, mais c'est le fichier que j'utilise depuis l'autre fois, c'était déjà le cas. Il faut tout mettre en ordre pour une simulation en conditions réelles. Mais ça a l'air d'aller bien, en tous cas à vide. A voir en charge maintenant! Là je vais me coucher, on verra plus tard. -------------------- "Détourne-toi des préceptes de ceux qui spéculent sur le monde, mais dont les idées ne sont pas confirmées par l'expérience."

Léonard de Vinci |

|

Ecrit le: Jeudi 18 Février 2016 à 00h53

|

|

Expert(e)       Groupe: Membres Messages: 255 Membre n°: 2 Inscrit le: 07/08/2002 |

-------------------- "Détourne-toi des préceptes de ceux qui spéculent sur le monde, mais dont les idées ne sont pas confirmées par l'expérience."

Léonard de Vinci |

|

Ecrit le: Jeudi 18 Février 2016 à 10h13

|

|

Expert(e)       Groupe: Membres Messages: 1561 Membre n°: 10313 Inscrit le: 11/03/2013 |

Bravo P. pour tes avancées sur les modèles spice.

Voici un montage rapide en simul, que j’utilise pour tester les MOS avec le 2153. En vert, le Vgate du transistor du bas, il ne faut pas atteindre 4V pour ne pas que les 2 transistors conduisent en même temps et dans l'idéal il faut une petite marge de sécurité sur cette pointe de Vgate. ici simul avec le STP8NM60 que j'ai selectioné pour sa faible charge de gate: 13nC  Et voilà ce que ça donne avec le SiHP25N50E  Je suis étonné que le pic de vgate soit si bas avec le SiHP25N50E.(modèle réalisé par P.) C’est ce transistor qui donne le plus bas résultat de pic sur VGate pour les transistors à fort VDS . Il est donc le meilleur. Ca vaudrait le coup de tester l’IRFP450 avec un modèle simplifié (à ce que j’en comprend ?) pour comparer. Pour voir si le problème sur Vgate persiste ou non avec un modèle simplifié. EDIT:je viens de simuler les SiHP25N50E, avec R9 = 12 Ohms et on a puissance moyenne dans la resistance 1.8KW et puissance moyenne dans chaque transistor 5W. Ca implique un rendement de l'étage de sortie proche de 100%. ou le modèle est optimiste ou le transistor est vraiment excellent. schema test joint Fichier joint ( Nombre de téléchargements: 3 )  test_MOS_sur_IR2153.asc (4.08 Ko)

test_MOS_sur_IR2153.asc (4.08 Ko) |

|

Ecrit le: Jeudi 18 Février 2016 à 15h40

|

|

Expert(e)       Groupe: Membres Messages: 3939 Membre n°: 10047 Inscrit le: 07/11/2011 |

A partir de quand voulez-vous simuler le schema final ? Celui avec tous les besttpractices implémentés ?

-------------------- « No matter where you are, Look for the brightest star, Believe it is true, My soul is smiling at you", FastWalkers

|

|

Ecrit le: Jeudi 18 Février 2016 à 18h15

|

|||

Expert(e)       Groupe: Membres Messages: 1561 Membre n°: 10313 Inscrit le: 11/03/2013 |

Bah en fait, vu où on en est, je considère que l’IRF2153 ne convient pas. Essentiellement parce qu’il n’y a pas de gestion du courant utile dans les transistors en fonction de la charge. Donc pas seulement à cause du risque de courant entre les 2 transistors. C’est ennuyeux car au démarrage le cockroft est quasiment un court circuit. J’ai voulu limiter les dégâts avec une résistance R9 mais c’est elle qui prend les Watts, surtout si la sortie dissipe 500W. il ne me parait pas envisageable d’avoir une résistance qui dissipe 250W par exemple. Ce n’est pas la bonne façon de faire pour passer de la puissance comme nous le souhaitons. Reste à voir ce que donne le cockroft équipé de résistances en série avec les diodes, en terme de charge. Peut être peut-on se passer de R9 mais ça reste encore hasardeux pour maîtriser le courant utile dans les transistors ? Ma préférence irait pour un circuit qui gère le courant dans les transistors, style SG3525. Et un schéma push pull pour utiliser des driver « low side » qui sont les meilleurs en terme de courant. Avec ce genre de driver à priori plus aucun problème avec quasiment n’importe quel transistor. Il n’y aura pas de pic de VGS risquant le passage de courant d’un transistor à l’autre. Il faut trouver des modèles qui tournent sans erreur sous LTspices pour le SG3525 , TC4452 (excellent driver) et choisir un transistor qui tient plus de 650V + marge, à cause du schéma push pull) Vérifier que le primaire à point milieu est bobinable sur le transfo THT, ce qui implique de définir ce primaire avec précision. Faire un schéma et le simuler. Ça me plait de travailler sur le sujet, on apprend des choses mais là je m’essouffle un peu a repartir sur un autre schéma. |

||

2 utilisateur(s) sur ce sujet (2 invités et 0 utilisateurs anonymes)

0 membres:

Pages: (11) « Première ... 7 8 [9] 10 11 Pages: (11) « Première ... 7 8 [9] 10 11 |

|

[ Script Execution time: 0.1934 ] [ 12 queries used ] [ GZIP activé ]